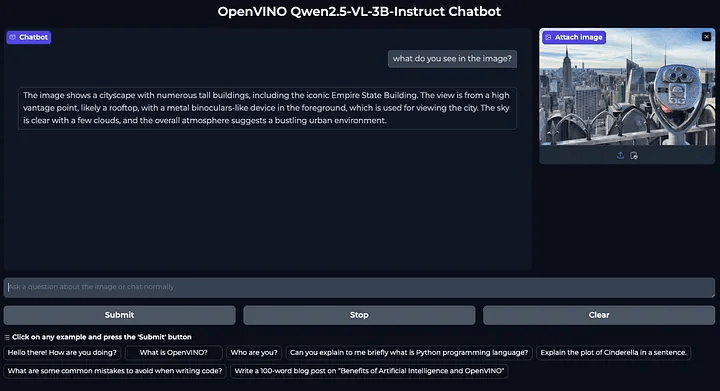

A Inteligência Artificial deixou de ser uma promessa distante para se tornar uma ferramenta concreta de transformação em áreas essenciais da sociedade. Na saúde, esse movimento é ainda mais relevante, porque envolve vidas, tempo de atendimento, qualidade na triagem, apoio aos profissionais e proteção de dados extremamente sensíveis. É nesse contexto que nasce a IA MED, uma solução desenvolvida pela MultiCortex para levar modelos avançados de linguagem ao setor de saúde com foco em precisão, privacidade, eficiência operacional e soberania tecnológica.

A IA MED já está em funcionamento na cidade de Bebedouro, interior de São Paulo, cidade natal de Alessandro de Oliveira Faria, também conhecido como Cabelo, fundador da MultiCortex. A implantação tem um significado especial: além de representar um avanço tecnológico para a rede municipal de saúde, simboliza o retorno de décadas de pesquisa, desenvolvimento e inovação para beneficiar diretamente a população da cidade onde nasceu o idealizador da solução.

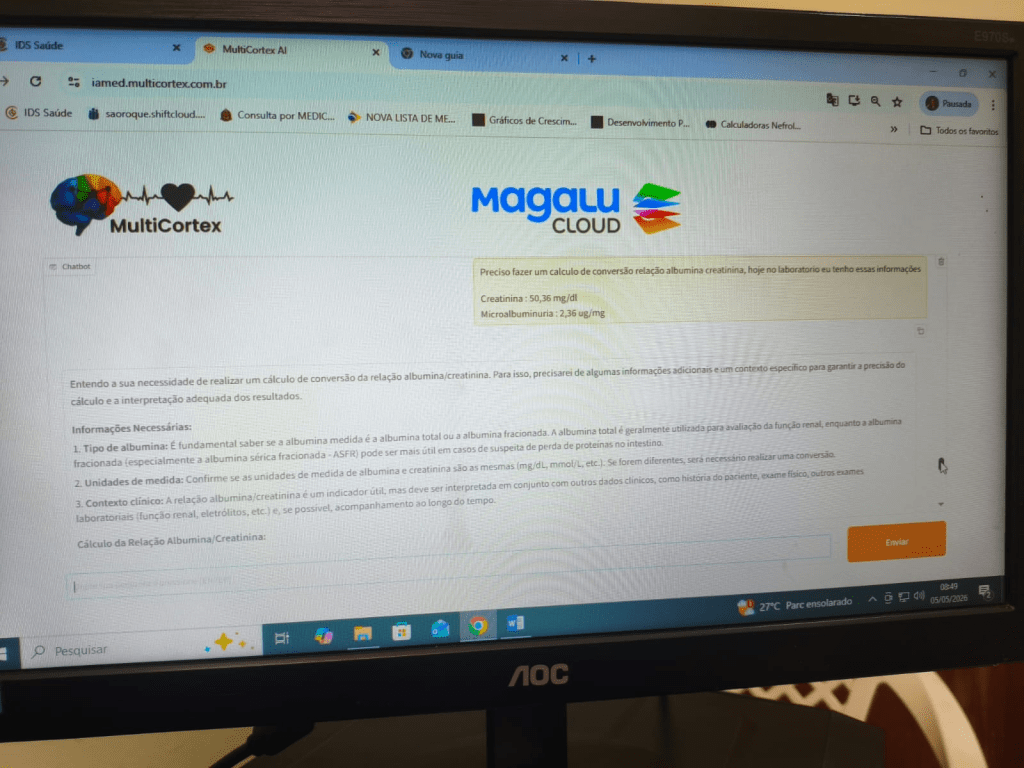

Segundo publicação oficial da Prefeitura Municipal de Bebedouro, a tecnologia IAmed foi desenvolvida pelo bebedourense e tem como objetivo auxiliar os profissionais de saúde no dia a dia, contribuindo para mais agilidade, precisão e qualidade nos atendimentos prestados à população. A Prefeitura também informa que a ferramenta foi cedida gratuitamente ao município pela MultiCortex IA, com infraestrutura Magalu Cloud, para acelerar e fomentar o uso de IA na saúde pública local.

A proposta da IA MED parte de uma preocupação muito concreta: ferramentas genéricas de Inteligência Artificial generativa, especialmente aquelas hospedadas em nuvens internacionais, não foram concebidas originalmente para lidar com a complexidade, a responsabilidade e a sensibilidade dos dados de saúde pública brasileira. Em um ambiente clínico, dados pessoais, históricos médicos, sintomas, exames, hipóteses, encaminhamentos e informações familiares não podem ser tratados como simples entradas de texto em uma aplicação qualquer. Eles exigem governança, segurança, rastreabilidade, controle de acesso e conformidade com a legislação brasileira.

A Lei Geral de Proteção de Dados Pessoais, a LGPD, estabelece regras para o tratamento de dados pessoais, inclusive em meios digitais, com o objetivo de proteger direitos fundamentais como liberdade, privacidade e livre desenvolvimento da personalidade. A própria legislação brasileira classifica dados referentes à saúde como dados pessoais sensíveis, o que torna ainda mais importante a adoção de arquiteturas tecnológicas que reduzam exposição, transferência desnecessária e dependência de ambientes fora do controle da organização pública ou privada.

Por isso, a IA MED foi pensada como uma Inteligência Artificial privada, verticalizada e adequada ao contexto da saúde. Diferente de IAs genéricas, que tentam responder sobre qualquer assunto a partir de modelos amplos e de uso geral, a IA MED trabalha com modelos de linguagem especializados, ajustados para fluxos, protocolos, terminologias e necessidades do setor de saúde. Essa verticalização permite maior aderência ao domínio médico-assistencial e reduz a dependência de respostas genéricas, vagas ou pouco contextualizadas.

Na prática, isso significa que a IA MED não existe para substituir médicos, enfermeiros, técnicos ou gestores de saúde. Pelo contrário: ela foi criada para apoiar esses profissionais. O papel da Inteligência Artificial é atuar como uma camada de auxílio, ajudando na organização das informações, na análise de dados clínicos disponíveis, na identificação de riscos, na triagem de prioridades, na sugestão de caminhos com base em protocolos e na redução de tarefas burocráticas que consomem tempo das equipes.

Nas Unidades Básicas de Saúde, onde a demanda é constante e os profissionais precisam lidar com grande volume de atendimentos, a IA pode se tornar uma aliada estratégica. Ela pode ajudar a estruturar informações do paciente, facilitar o acesso ao histórico, apoiar a classificação de risco, sugerir perguntas relevantes durante uma triagem, organizar encaminhamentos e permitir que a equipe tenha uma visão mais clara do fluxo de atendimento. Com isso, o profissional de saúde ganha tempo, reduz carga mental e pode se concentrar mais no cuidado humano.

Essa é uma das maiores contribuições da IA MED: usar tecnologia não para afastar o paciente do profissional, mas para devolver tempo ao atendimento humanizado. A saúde pública enfrenta desafios diários de volume, urgência, documentação, filas, registros e priorização. Quando uma ferramenta de IA bem desenhada assume parte do trabalho repetitivo e auxilia na organização das informações, ela contribui para que médicos e enfermeiros possam tomar decisões com mais segurança e menos sobrecarga.

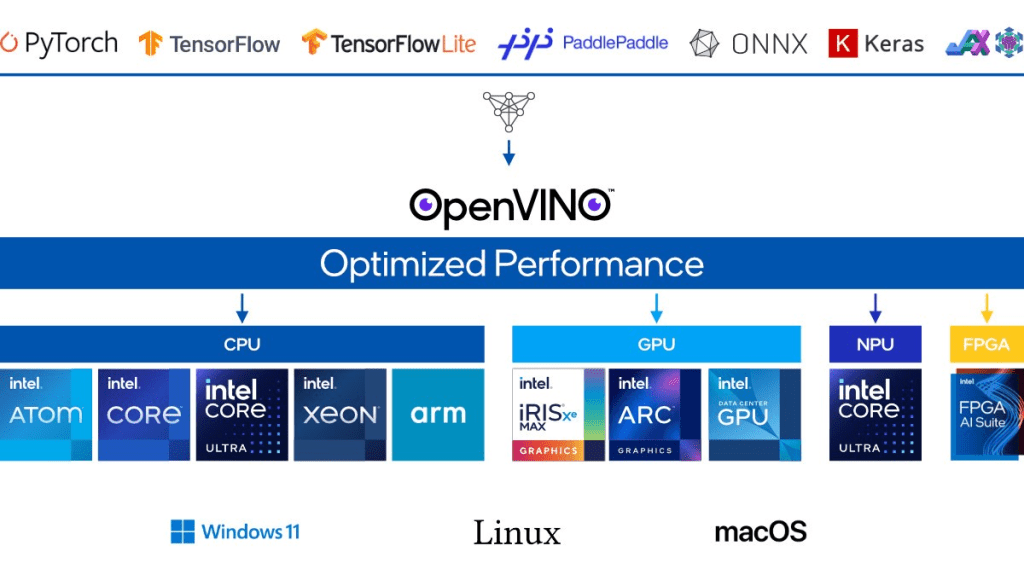

Outro diferencial importante da IA MED está no custo computacional. Muitos projetos de Inteligência Artificial são inviabilizados porque dependem de servidores extremamente caros, como máquinas baseadas em GPUs H100 ou B200, que podem representar investimentos muito altos em infraestrutura. A proposta da MultiCortex é demonstrar que, com engenharia especializada, otimização de modelos, verticalização e uso inteligente de hardware, é possível entregar uma solução de IA aplicada à saúde utilizando infraestrutura com custo muito inferior na ordem de aproximadamente 10% do valor de grandes servidores baseados nessas GPUs topo de linha (GRAÇAS A COMPUTAÇÃO HETEROGÊNEA).

Essa diferença de custo é fundamental para a realidade brasileira. A inovação não pode ficar restrita a grandes centros, grandes hospitais ou instituições com orçamentos milionários. A Inteligência Artificial precisa ser viável para municípios, unidades públicas, clínicas, secretarias e organizações que buscam modernização, mas precisam respeitar limites financeiros. A IA MED nasce justamente dessa visão: criar uma tecnologia de alto impacto, com custo mais acessível e aplicação prática no cotidiano da saúde

A parceria com a Magalu Cloud reforça outro ponto central do projeto: a soberania dos dados. A Magalu Cloud se apresenta como uma nuvem brasileira, com preços em reais, suporte em português, infraestrutura local e data centers fisicamente no Brasil, distribuídos nas regiões Sudeste e Nordeste. A empresa também destaca que os dados são armazenados localmente e em conformidade com a legislação brasileira.

Para aplicações de saúde, esse detalhe é decisivo. Utilizar infraestrutura em território nacional reduz riscos associados à transferência internacional de dados, melhora a previsibilidade regulatória e aproxima a operação da realidade jurídica, técnica e institucional do Brasil. Em vez de depender exclusivamente de nuvens estrangeiras, cobradas em dólar e sujeitas a camadas adicionais de complexidade contratual e regulatória, a IA MED utiliza uma infraestrutura alinhada ao conceito de soberania digital.

A Magalu Cloud também destaca benefícios como preços em reais, previsibilidade sem variação cambial, suporte humano em português, infraestrutura local, baixa latência, custos reduzidos, escalabilidade e serviços como máquinas virtuais, armazenamento, VPC, Kubernetes, banco de dados e ferramentas de identidade e acesso. Para um projeto como a IA MED, esses elementos ajudam a compor uma base tecnológica mais adequada para o setor público brasileiro.

Além da privacidade, há também a questão da previsibilidade de custos. Muitas soluções de IA em nuvem funcionam com cobrança baseada em tokens, o que pode se tornar um problema quando há grande volume de atendimentos, consultas, registros e interações. Em ambientes públicos, onde orçamento precisa ser planejado e justificado, custos variáveis e imprevisíveis podem dificultar a adoção em escala. A IA MED busca reduzir esse problema ao operar em uma arquitetura mais controlada, privada e otimizada, sem depender do modelo tradicional de cobrança por token de plataformas externas.

Essa abordagem permite que a Inteligência Artificial deixe de ser uma despesa imprevisível e passe a ser uma infraestrutura estratégica. Em vez de pagar indefinidamente por cada interação processada em serviços de terceiros, a organização pode trabalhar com um ambiente mais previsível, controlado e adaptado à sua demanda. Para a saúde pública, isso significa maior capacidade de planejamento, menor dependência externa e mais sustentabilidade para expandir o uso da tecnologia.

O impacto para a população pode ser percebido de várias formas. O cidadão tende a se beneficiar de atendimentos mais organizados, triagens mais ágeis, melhor acompanhamento, redução de retrabalho e maior apoio à identificação de prioridades. Em muitos casos, a diferença não estará apenas em “usar IA”, mas em usar IA para melhorar processos invisíveis que afetam diretamente a experiência do paciente: tempo de espera, clareza das informações, encaminhamentos, continuidade do cuidado e segurança no atendimento.

Para os profissionais de saúde, a IA MED representa uma ferramenta de apoio em um cenário de alta responsabilidade. O cansaço mental, a pressão por produtividade, a repetição de tarefas administrativas e o volume de informações podem aumentar a margem de erro em qualquer setor. Na saúde, porém, erros podem ter consequências graves. A Inteligência Artificial, quando aplicada com responsabilidade, pode ajudar a mitigar riscos, organizar dados e apoiar decisões, sempre mantendo o profissional humano no centro do processo.

A iniciativa em Bebedouro também carrega um valor simbólico importante. Ver uma tecnologia criada por um bebedourense sendo aplicada diretamente em benefício da população local mostra que inovação não precisa nascer apenas em polos internacionais ou grandes capitais. A inovação também pode surgir do interior, de trajetórias individuais de pesquisa, de comunidades técnicas brasileiras e de empresas que entendem os desafios reais do país.

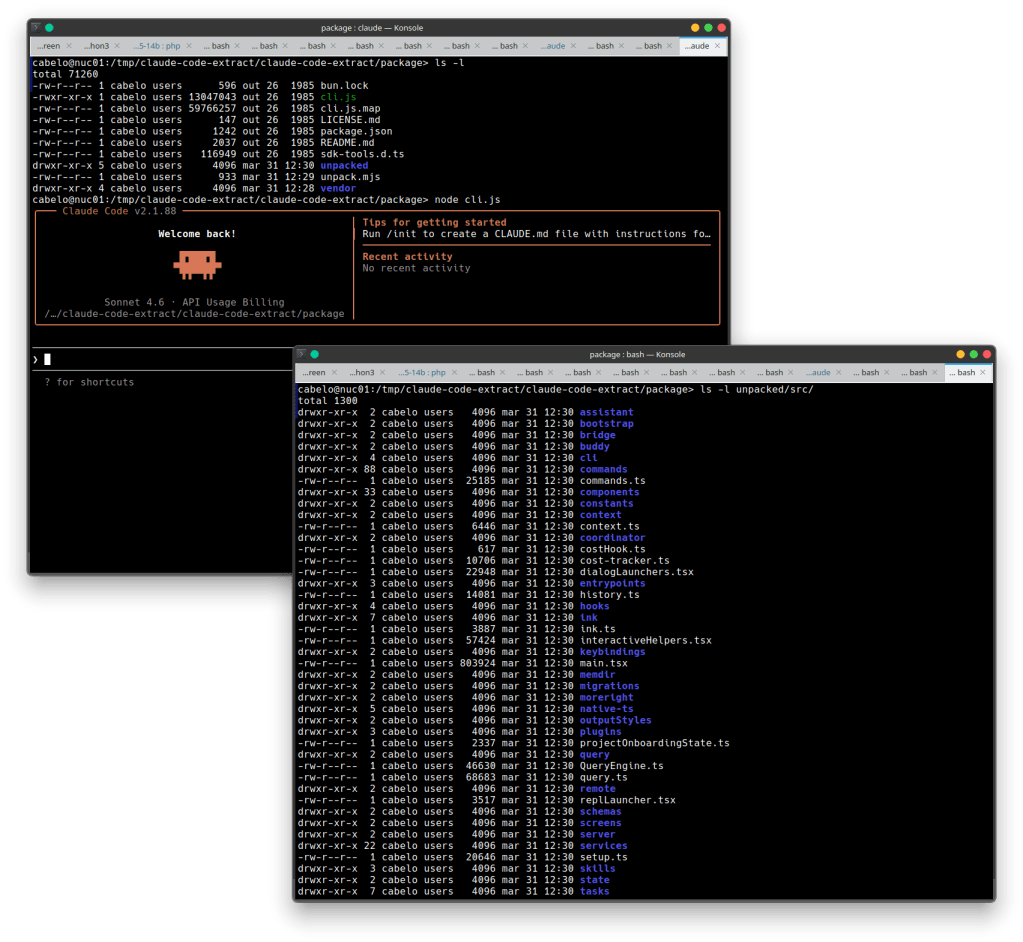

Para Alessandro de Oliveira Faria, a implantação da IA MED em Bebedouro representa mais do que um projeto tecnológico. É o resultado de mais de 25 anos de pesquisa em Inteligência Artificial, iniciada ainda em 1998, somada a uma trajetória dedicada à computação de alto desempenho, otimização de hardware, software livre e aplicação prática da tecnologia em benefício da sociedade. Levar essa experiência para a saúde pública da sua cidade natal é uma forma de transformar conhecimento acumulado em impacto social direto.

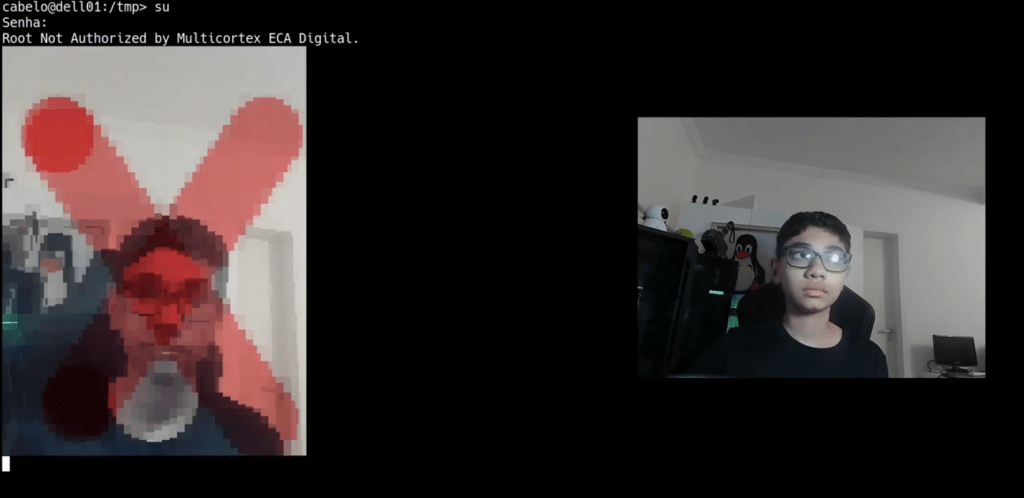

Durante a fase de avaliação, a MultiCortex disponibilizou o sistema gratuitamente ao município de Bebedouro por meio de um termo de cooperação com a Prefeitura. A empresa assumiu integralmente os custos computacionais em nuvem, reforçando o compromisso de manter Bebedouro na vanguarda da inovação tecnológica. A iniciativa remete ao histórico da cidade com projetos pioneiros de tecnologia, como ocorreu no início dos anos 2000 com a implantação da biometria de impressão digital.

Esse ponto é essencial: inovação pública não acontece apenas quando se compra tecnologia pronta. Ela acontece quando há colaboração entre poder público, empresas, pesquisadores, profissionais técnicos e a comunidade. Ao ceder a IA MED gratuitamente na fase de avaliação, a MultiCortex cria uma oportunidade concreta para que a cidade experimente, valide e compreenda os benefícios da Inteligência Artificial aplicada à saúde de forma segura, responsável e alinhada à realidade local.

A IA MED também reforça uma visão maior da MultiCortex: devolver às organizações o controle sobre sua própria Inteligência Artificial. No setor da saúde, esse controle é ainda mais importante. Não se trata apenas de desempenho técnico, mas de governança, soberania, privacidade e responsabilidade. Uma IA aplicada à saúde precisa respeitar dados, pessoas, profissionais e instituições. Precisa ser explicável dentro do possível, auditável, segura e construída para o contexto em que será usada.

Ao unir modelos de LLM verticalizados, infraestrutura nacional, custo computacional reduzido, privacidade e foco no apoio aos profissionais de saúde, a IA MED se posiciona como uma alternativa brasileira para um dos maiores desafios da atualidade: como usar Inteligência Artificial em áreas sensíveis sem abrir mão da segurança, da ética e da soberania dos dados.

Bebedouro, ao receber essa implantação, dá um passo importante rumo à modernização dos serviços públicos de saúde. A iniciativa mostra que a tecnologia pode ser uma aliada direta do cuidado, não apenas uma ferramenta distante de laboratório. Mostra também que a IA pode ser aplicada de forma responsável, com foco em pessoas, em eficiência pública e na valorização dos profissionais que estão na linha de frente.

A IA MED nasce com esse propósito: transformar a Inteligência Artificial em uma infraestrutura confiável para a saúde, capaz de apoiar decisões, otimizar processos, reduzir custos e proteger dados sensíveis. Mais do que uma ferramenta tecnológica, ela representa uma visão de futuro para a saúde pública brasileira, um futuro em que inovação, privacidade, soberania e cuidado humano caminham juntos.